一。FPGA使用的电源类型

FPGA电源要求输出电压范围从1.2V到5V,输出电流范围从数十毫安到数安培。可用三种电源:低压差(LDO)线性稳压器、开关式DC-DC稳压器和开关式电源模块。最终选择何种电源取决于系统、系统预算和上市时间要求。

如果电路板空间是首要考虑因素,低输出噪声十分重要,或者系统要求对输入电压变化和负载瞬变做出快速响应,则应使用LDO稳压器。LDO功效比较低(因为是线性稳压器),只能提供中低输出电流。输入电容通常可以降低LDO输入端的电感和噪声。LDO输出端也需要电容,用来处理系统瞬变,并保持系统稳定性。也可以使用双输出LDO,同时为VCCINT和VCCO供电。

如果在设计中效率至关重要,并且系统要求高输出电流,则开关式稳压器占优势。开关电源的功效比高于LDO,但其开关电路会增加输出噪声。与LDO不同,开关式稳压器需利用电感来实现DC-DC转换。

二。FPGA的特殊电源要求

为确保正确上电,内核电压VCCINT的缓升时间必须在制造商规定的范围内。对于一些FPGA,由于VCCINT会在晶体管阈值导通前停留更多时间,因此过长的缓升时间可能会导致启动电流持续较长时间。如果电源向FPGA提供大电流,则较长的上电缓升时间会引起热应力。ADI公司的DC-DC稳压器提供可调软启动,缓升时间可以通过外部电容进行控制。缓升时间典型值在20ms至100ms范围内。

许多FPGA没有时序控制要求,因此VCCINT、VCCO和VCCAUX可以同时上电。如果这一点无法实现,上电电流可以稍高。时序要求依具体FPGA而异。对于一些FPGA,必须同时给VCCINT和VCCO供电。对于另一些FPGA,这些电源可按任何顺序接通。多数情况下,先给VCCINT后给VCCO供电是一种较好的做法。

当VCCINT在0.6V至0.8V范围内时,某些FPGA系列会产生上电涌入电流。在此期间,电源转换器持续供电。这种应用中,因为器件需通过降低输出电压来限制电流,所以不推荐使用返送电流限制。但在限流电源解决方案中,一旦限流电源所供电的电路电流超过设定的额定电流,电源就会将该电流限制在额定值以下。

三。FPGA配电结构

1.集中式电源结构

对于高速、高密度FPGA器件,保持良好的信号完整性对于实现可靠、可重复的设计十分关键。适当的电源旁路和去耦可以改善整体信号完整性。如果去耦不充分,逻辑转换将会影响电源和地电压,导致器件工作不正常。此外,采用分布式电源结构也是一种主要解决方案,给FPGA供电时可以将电源电压偏移降至最低。

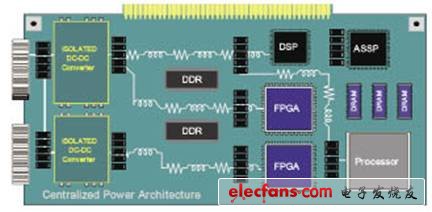

在传统电源结构中,AC/DC或DC/DC转换器位于一个地方,并提供多 个输出电压,在整个系统内分配。这种设计称为集中式电源结构 (CPA),见图1。以高电流分配低电压时,铜线或PCB轨道会产生严重的电阻损耗,CPA就会发生问题。

图1 集中式电源结构

2.分布式电源结构

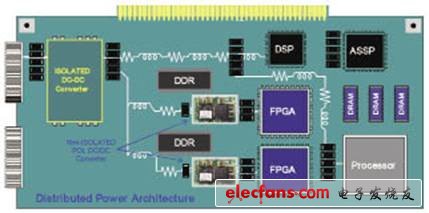

CPA的替代方案是分布式电源结构(DPA),见图2。采用DPA时,整个系统内仅分配一个半稳压的DC电压,各DC/DC转换器(线性或开关式)与各负载相邻。DPA中,DC/DC转换器与负载(例如FPGA)之间的距离近得多,因而线路电阻和配线电感引起的电压下降得以减小。这种为负载提供本地电源的方法称为负载点(POL)。

图2 分布式电源结构