高速数字电路电源系统的电磁兼容研究

[发布时间]:2010年7月27日

[来源]:电子变压器资讯网

[点击率]:42766

【导读】: 随着实时信号处理的速率不断加快,数字电路系统的时钟频率也随之增加。同时,半导体工艺的改进,也使得电路系统中信号边沿速率提升到ns级甚至更高的级别。快速的信号边沿变化使得电路信号产生振铃、反射、串扰...

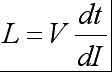

在高频(几百MHz)范围内,采用减少寄生电感的方式比提高电容值更有效一些。限制最大的电感量可以使纹波电压达到最小:

(10)

(10)

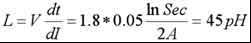

其中,dt是瞬态电流的最快上升时间。假设一个2A的电流有着1ns的上升时间,电源分布系统保证1.8V电源供电5%以内的纹波。允许的电感量估算如下:

(11)

(11)

投稿箱:

电子变压器、电感器、磁性材料等磁电元件相关的行业、企业新闻稿件需要发表,或进行资讯合作,欢迎联系本网编辑部QQ:

, 邮箱:

info%ett-cn.com (%替换成@)。

第一时间获取电子变压行业资讯,请在微信公众账号中搜索“电子变压器资讯”或者“dzbyqzj”,或用手机扫描左方二维码,即可获得电子变压器资讯网每日精华内容推送和最优搜索体验,并参与活动!

温馨提示:回复“1”获取最新资讯。

如果你对资讯频道有任何意见或建议,请到前往反馈平台给我们留言。

【我要提建议】